With the exploitation of parallelism and the consequent exponential growth in performance in recent decades, multiprocessor chips (CMP) manufacture is increasing in complexity. CMPs require communication between their cores. Architectures based on messages provide the processor with a local memory that can only be accessed by it, requiring message exchange with the other cores in the system. Architectures based on shared memory make all memory addresses accessible to all cores, enabling communication through loads and stores. The abstraction of a single shared memory requires a conceptual model of memory operations that can be executed simultaneously, so-called Memory Consistency Model (MCM).

In the ever-increasing quest to increase performance, multicore chip manufacturers started to use increasingly relaxed MCMs, where read and write instructions can be executed out-of-the-order specified by the threads of a concurrent program. The growing number of processing cores and the use of relaxed consistency models corroborate the increased complexity of processor designs, making them susceptible to design errors.

Functional verification, in an informal way, is the comparison of what the processor should ideally be and what it currently is. In the context of CMPs, the verification process consists of running concurrent programs on multi-chip simulators and assessing whether the behavior observed corresponds to the expected behavior. Such programs are created automatically by intelligent agents, and the behavior of the MCM of the chip(s) is also automatically evaluated by checkers afterwards (post-morten) or during execution (on-the-fly).

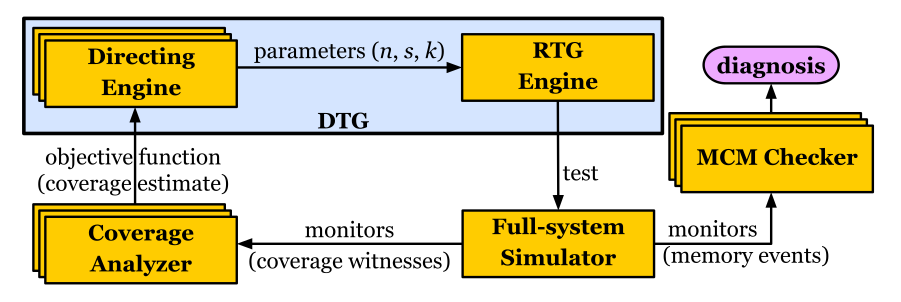

During more than a decade of research, ECL has developed a complex but efficient shared memory functional verification framework. The framework consists of an automatic generator of concurrent programs, a checker, and intelligent agents that direct the automatic creation of tests to reduce verification time and effort by exploiting the characteristics of this problem. Each concurrent program is executed on a multicore, stimulating the shared memory system. The checker automatically verifies whether, when running the program, any observed behavior has disobeyed the multicore’s memory model, which represents a hardware error.

After more than a decade of publications, ECL’s multicore testing group continues to work on automatic test generation to reduce verification time and effort, creating new forms of test representation and intelligent algorithms. In addition to porting the framework for Instruction Set Architectures to SPARC and ARM, RISC-V has emerged as a target for porting and publications.

From this area of research, ECL has produced doctoral theses, master’s dissertations, and scientific initiation projects, publishing high scientific level works and forming qualified professionals, working on AI research in Brazil, as well as in companies in Europe and the United States.

Publications (until 2023):

E. A. Rambo, O. P. Henschel and L. C. V. dos Santos, “Automatic generation of memory consistency tests for chip multiprocessing,” 2011 18th IEEE International Conference on Electronics, Circuits, and Systems, Beirut, Lebanon, 2011, pp. 542-545, doi: 10.1109/ICECS.2011.6122332.

L. S. Freitas, G. A. G. Andrade and L. C. V. dos Santos, “Efficient verification of out-of-order behaviors with relaxed scoreboards,” 2012 IEEE 30th International Conference on Computer Design (ICCD), Montreal, QC, Canada, 2012, pp. 510-511, doi: 10.1109/ICCD.2012.6378698.

E. A. Rambo, O. P. Henschel and L. C. V. dos Santos, “On ESL verification of memory consistency for system-on-chip multiprocessing,” 2012 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, Germany, 2012, pp. 9-14, doi: 10.1109/DATE.2012.6176424.

L. S. Freitas, G. A. G. Andrade and L. C. V. dos Santos, “A template for the construction of efficient checkers with full verification guarantees,” 2012 19th IEEE International Conference on Electronics, Circuits, and Systems (ICECS 2012), Seville, Spain, 2012, pp. 280-283, doi: 10.1109/ICECS.2012.6463746.

L. S. Freitas, E. A. Rambo and L. C. V. dos Santos, “On-the-fly verification of memory consistency with concurrent relaxed scoreboards,” 2013 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 2013, pp. 631-636, doi: 10.7873/DATE.2013.138.

O. P. Henschel and L. C. V. dos Santos, “Pre-silicon verification of multiprocessor SoCs: The case for on-the-fly coherence/consistency checking,” 2013 IEEE 20th International Conference on Electronics, Circuits, and Systems (ICECS), Abu Dhabi, United Arab Emirates, 2013, pp. 843-846, doi: 10.1109/ICECS.2013.6815546

G. A. G. Andrade, M. Graf and L. C. V. dos Santos, “Chain-based pseudorandom tests for pre-silicon verification of CMP memory systems,” 2016 IEEE 34th International Conference on Computer Design (ICCD), Scottsdale, AZ, USA, 2016, pp. 552-559, doi: 10.1109/ICCD.2016.7753340.

G. A. G. Andrade, M. Graf, N. Pfeifer and L. C. V. dos Santos, “Steep Coverage-Ascent Directed Test Generation for Shared-Memory Verification of Multicore Chips,” 2018 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), San Diego, CA, USA, 2018, pp. 1-8, doi: 10.1145/3240765.3240852.

G. A. G. Andrade, M. Graf and L. C. V. dos Santos, “Chaining and Biasing: Test Generation Techniques for Shared-Memory Verification,” in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 39, no. 3, pp. 728-741, March 2020, doi: 10.1109/TCAD.2019.2894376.

M. Graf, O. P. Henschel, R. P. Alevato and L. C. V. dos Santos, “Spec&Check: An Approach to the Building of Shared-Memory Runtime Checkers for Multicore Chip Design Verification,” 2019 IEEE/ACM International Conference on Computer-Aided Design (ICCAD), Westminster, CO, USA, 2019, pp. 1-7, doi: 10.1109/ICCAD45719.2019.8942040.

G. A. G. Andrade, M. Graf, N. Pfeifer and L. C. V. dos Santos, “A Directed Test Generator for Shared-Memory Verification of Multicore Chip Designs,” in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 39, no. 12, pp. 5295-5303, Dec. 2020, doi: 10.1109/TCAD.2020.2974343.

N. Pfeifer, B. V. Zimpel, G. A. G. Andrade and L. C. V. dos Santos, “A Reinforcement Learning Approach to Directed Test Generation for Shared Memory Verification,” 2020 Design, Automation & Test in Europe Conference & Exhibition (DATE), Grenoble, France, 2020, pp. 538-543, doi: 10.23919/DATE48585.2020.9116198.

M. Graf, G. A. G. Andrade and L. C. V. dos Santos, “EveCheck: An Event-Driven, Scalable Algorithm for Coherent Shared Memory Verification,” in IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 42, no. 2, pp. 683-696, Feb. 2023, doi: 10.1109/TCAD.2022.3178051.