Os circuitos integrados (CIs) ou “chips” estão presentes em praticamente todos os aparelhos eletrônicos da atualidade. Os projetos de circuitos digitais, como processadores ou codificadores de vídeo, requerem um número muito grande de transistores para serem implementados, caracterizando circuitos VLSI (Very Large Scale Integration). O projeto desse tipo de circuito é feito com base em um fluxo de projeto (digital flow), o qual é definido por diferentes etapas.

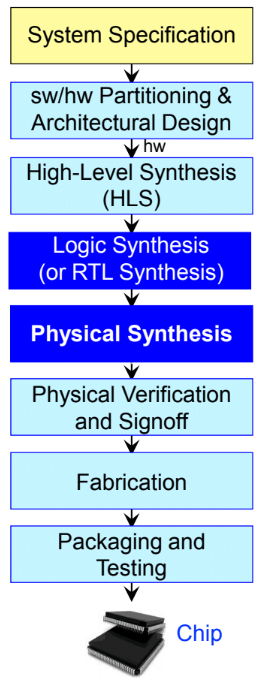

Na concepção de um projeto, realiza-se inicialmente a especificação do sistema a ser projetado: entradas e saídas, funcionalidade, blocos principais, dentre outros. Em seguida, define-se quais partes do sistema serão desenvolvidas em software e quais delas serão elaboradas em hardware. Para a parte em hardware, inicia-se então aplicação do fluxo de projeto VLSI.

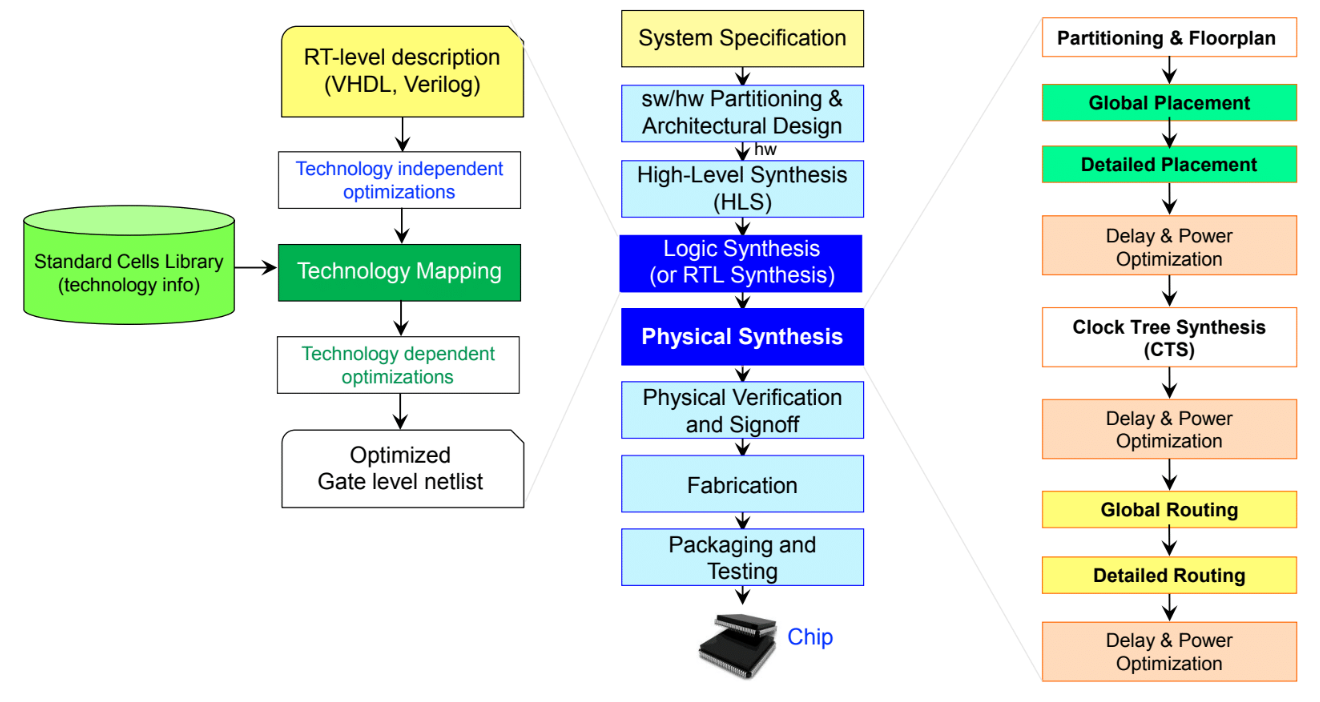

Primeiramente, a descrição do circuito é realizada utilizando linguagens de descrição de hardware (HDL), como Verilog ou VHDL. A funcionalidade do circuito é aferida por meio de uma simulação inicial sem atrasos e, caso não sejam encontrados problemas, o fluxo segue para a próxima etapa: a síntese lógica, em que a descrição do circuito gera um mapeamento de conexões (netlist) utilizando uma biblioteca de células padrão, que inclui portas lógicas, flip-flops, dentre outros componentes.

As informações sobre as células padrão estão definidas em PDKs (Process Design Kits), que são específicos para cada uma das tecnologias utilizadas, dependendo do nodo tecnológico (comprimento do canal dos transistores utilizados, como 65nm, 45nm, 28nm) e também da foundry em questão (TSMC, Global Foundries, entre outras).

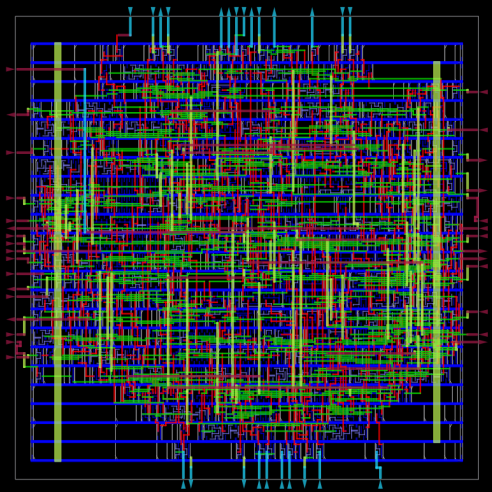

Após a síntese lógica acontece a síntese física, que consiste no processo de criação do layout do chip, incluindo etapas internas como o posicionamento das células, roteamento e a colocação de pads (conexões ao mundo externo). Uma nova simulação pode ser executada, considerando agora atrasos mais realistas das células utilizadas e das interconexões do circuito.

Por fim, o circuito ainda deve ser verificado segundo as regras de projeto para fabricação na tecnologia (DRC) e também a equivalência entre o layout obtido e o esquemático inicial desejado (LVS). Com o layout completo e validado, é possível realizar o envio do projeto para fabricação e posteriormente as etapas de packaging e testing dos novos chips.

Além das partes do fluxo destacadas acima, cabe mencionar que etapas intermediárias como Logical Equivalence Check (LEC), extração de parâmetros RC, dentre outras, também fazem parte do fluxo e são importantes para garantir o bom funcionamento do produto final. Todas as etapas de síntese são realizadas de forma automática pela ferramenta, bem como as verificações. Quanto às simulações, normalmente o projetista deverá desenvolver um testbench para teste da arquitetura, buscando validar o circuito com a melhor abrangência possível e evitando erros que poderiam levar à perda de muitos recursos com a fabricação de um chip defeituoso.

No ECL, nosso fluxo de projetos é feito com ferramentas de EDA Synopsys. Além disso, temos implementado também um fluxo de projeto digital para ASIC (circuitos integrados de aplicação específica) totalmente open source com ferramentas como Icarus Verilog, Yosys e OpenROAD Trabalhamos também com diferentes nodos tecnológicos, além de PDKs open source e privados de diversas foundries do mundo.