O trabalho intitulado How Deep Learning Can Drive Physical Synthesis Towards More Predictable Legalization, desenvolvido por Renan Netto, Sheiny Fabre, Tiago Augusto Fontana, Vinicius Livramento, Laércio Pilla, e José Luís Güntzel foi aceito para publicação no evento International Symposium on Physical Design em 2019, sendo um dos candidatos a best paper no mesmo evento.

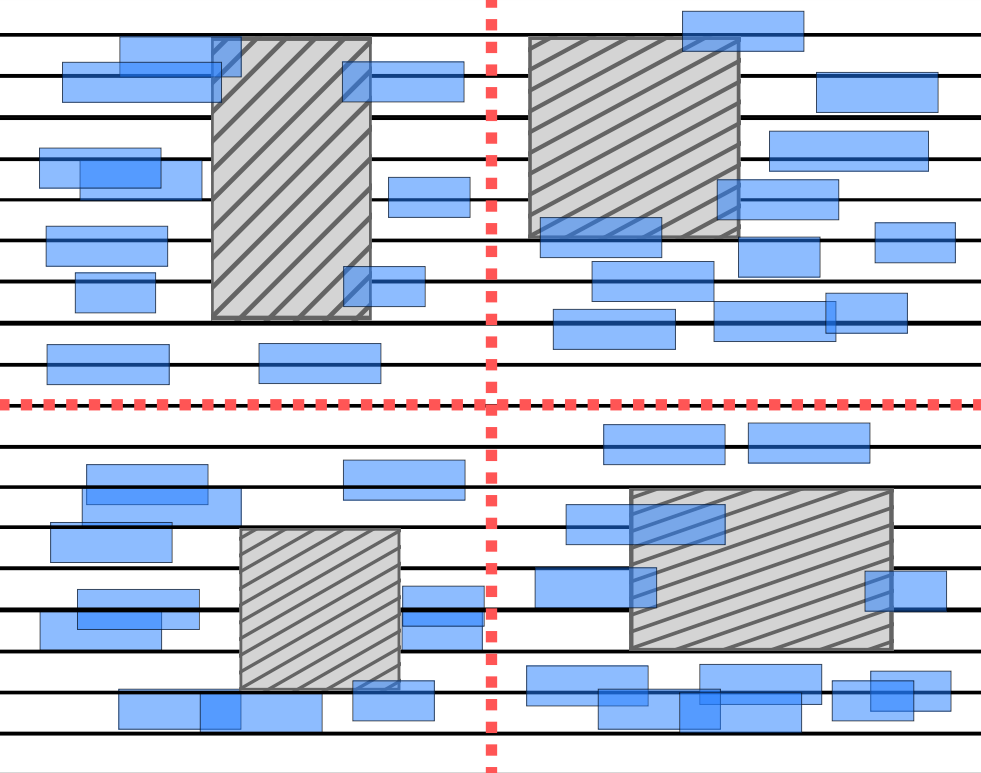

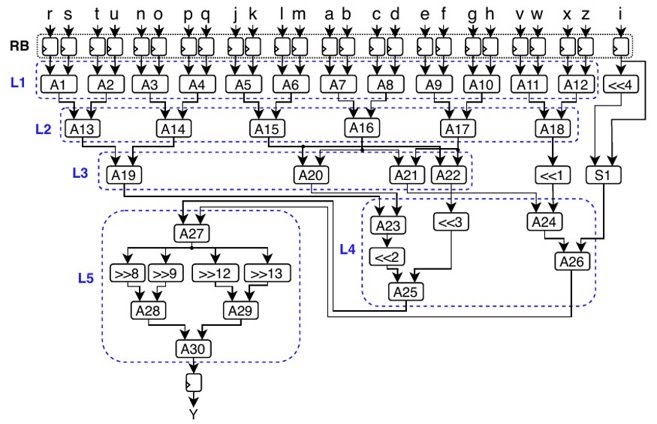

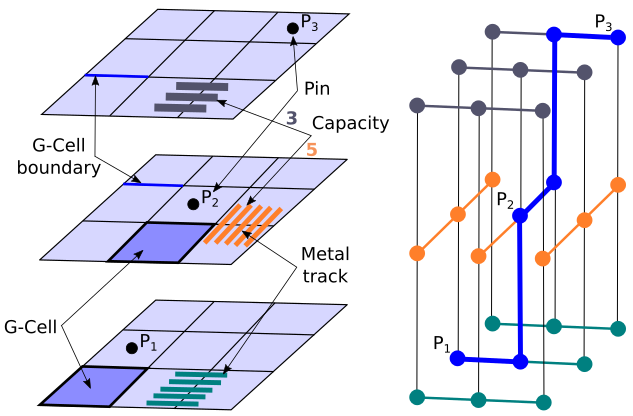

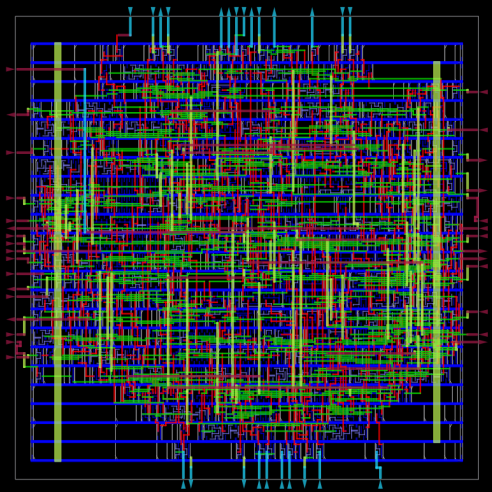

Esse trabalho trata do uso de redes neurais para identificar regiões com alto deslocamento de células durante a legalização de circuitos integrados.

O International Symposium on Physical Design é uma das principais conferências da área de EDA e physical design.